Modul III

Counter

Percobaan 3

Gambar 1. Jurnal Percobaan 3

2. Alat dan Bahan

[Kembali]

2.1 Alat [kembali]

a.. Jumper

Gambar 2. Jumper

b.Panel DL 2203D

c.Panel DL 2203C

d.Panel DL 2203S

Gambar 3. Modul De Lorenzo

2.2 Bahan (proteus) [kembali]

c. Power DC

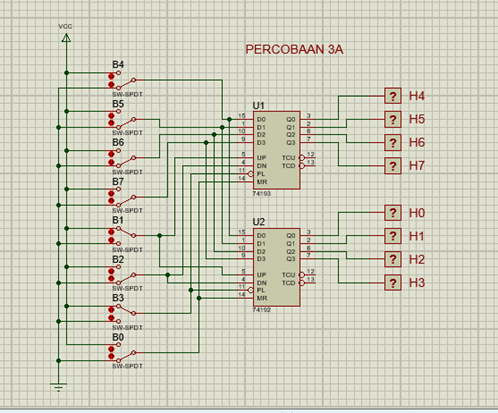

Gambar 9. Rangkaian percobaan 3a di proteus

Gambar 10. Rangkaian percobaan 3a

Gambar 12. Rangkaian percobaan 3a

Pada counter synchronus, clock dipasang secara paralel sehingga output bergulir secara berbarengan. Hal ini terlihat pada rangkaian bahwa sinyal clock diberikan pada CLK secara berbarengan.

Perbedaan antara IC74192 dan IC74193 adalah pada outputnya. Pada IC74192 output count dimulai dari 0-15 (hexadecimal) sedangkan IC74193 output count dimulai dari 0-9 (desimal).

Terlihat dari tabel percobaan ketika kaki MR (master reset) diberi logika 1 maka semua output akan tereset menjadi 0 (atau dalam binary 0 0 0 0). Sedangkan ketika kaki PL diberi logika 0 maka kaki PL akan aktif dimana PL akan aktif bila diberi logika 0 karena kakinya bersifat aktif low. Ketika PL akatif (diberi logika 0) maka output akan tergantung terhadap input D0, D1, D2, dan D3. Untuk mencounting counter up atau down bergantung terhadap kaki UP dan DN dimana ketika diberi input HIGH pada pin DN dan sinyal clock pada pin UP, maka counter akan dalam kondisi counter up,sedangkan ketika diberi input HIGH pada pin UP dan sinyal clock pada pin D maka counter akan dalam kondisi counter down.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Apa itu fungsi pin Tcu dan TCD? Bagaimana cara penerapannya?

Jawab:

TCU berfungsi untuk mengindikasi bahwa perhitungan mencapai nilai maksimum (9 untuk LS192 dan 15 untuk LS193) dalam mode up counting. Sedangkan, TCD berfungsi untuk mengindikasi bahwa saat perhitungan mencapai nilai minimum dalam mode down counting.

Penerapan TCU:

ketika perhitungan mencapai angka maksimum, sinyal count up clock akan berubah dari tinggi ke rendah yang menyebabkan TCU berubah menjadi Low. TCU akan tetap low hingga sinyal count up clock kembali high yang mana menandakan dimulainya perhitungan kembali dari awal sehinggal TCU dapat mengendali operasi yang terkait Perubahan penghitungen maksimum.

Penerapan TCD:

ketika perhitungan mencapai angka minimum, Sinyal count down clock akan berubah dari high menjadi low yang menyebabkan TCD berubah menjadi low. TCD tetap low hingga count down clock kembali bernilai high yang menandakan dimulainya perhitungan kembali dari angka tertinggi

2. Apa Pengaruh gerbang OR pada rangkaian 3B?

Jawab:

- Gerbang OR1 terhubung kekaki UP berfungi untuk mengendali up counting. Ketika salah satu kaki input gerbang OR1 aktif maka output OR1 akan aktif dan diteruskan kekaki UP sehingga terjadi up counting.

- Gerbang OR2 terhubung kekaki DN berfungsi untuk mengendali down counting. Ketika salah satu input OR1 aktif maka output OR1 akan aktif ban diteruskan kekaki DN sehingga terjadi down counting.

3. Bagaimana Pengaruh pin MR pada rangkaian? Jelaskan menggunakan gambar rangkaian dalam dari IC tersebut!

Jawab:

Pengaruh pin MR (Master reset) pada IC 74192 dan 74193 adalah Ketika MR diberi input high, maka kaki MR aktif dan mereset output (Q0 = 0, Q1 = 0, Q2 = 0, dan Q3=0).

(atau jelasnya ada didatasheet)

Terlihat pada rangkaian dalam IC, ketika MR diberi logika 1 maka akan dibalikkan oleh gerbang NOT yang menghasilan output 0 kemudian dibalikkan sehingga menjadi 1 dan masuk kekaki input gerbang OR yang mana ketika salah satunya atau keduanya diberi input 1, maka output gerbang OR adalah 1 sehingga akan mengaktifkan kaki R yang akan mereset output flip-flop. Dikarenakan jika salah satu kaki OR berlogika 1 telah membuat output OR bernilai 1 sehingga kaki lain bernilai don't care. Begitu pula pada kondisi flip flop lainnya sehingga keempat flip-flop berlogika 0 (atau kondisi reset). Ketika MR berlogika 1 akan masuk kegerbang NOT sehingga output menjadi nol dan diteruskan kegerbang NAND dimana jika inputnya ada yang nol akan berlogika 1 sehingga kaki S tidak aktif dan yang aktif hanya kaki R untuk mereset output.

7. Link Download

[Kembali]

- Download HTML [klik disini]

- Download Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disini]

- Download Datasheet IC 74192 [klik disini]

- Download Datasheet IC 74193 [klik disini]

.png)